Products

With ever increasing bandwidth and speed requirements for enabling future technologies, SerDes (Serializer/De-Serializer) plays a vital component for any data communication. Terminus Circuits offers a one-stop-shop solution for all SerDes designing. Terminus Circuits provides the best-in-class SerDes IP across various nodes, multiple foundries and protocols.

Deliverables:

- • User and integration guides

- • Netlist

- • Timing library

- • Register map

- • Verilog

- • IBIS-AMI models

- • LEF views

- • Layout Versus Schematic (LVS)

- • Design Rule Check (DRC) reports

- • Silicon

Terminus Circuits offers unprecedented power savings and performance for customers requiring superior SerDes technology. Our SerDes IPs are available in the following nodes:.

16Gbps – TSMC 28HPC, TSMC 28HPC+

10Gbps - TSMC 65GP, TSMC 55LP

8Gbps – TSMC 65GP, TSMC 28 HPC, TSMC 28HPC+, GF 28SLP

5G/2.5Gbps – TSMC 28 HPC, TSMC 28HPC+, TSMC 65GP, TSMC 55LP, GF 28SLP

PCIe is the most common protocol in high speed serial standards to connect components in embedded systems. It leverages SerDes (Serializer/De-serializer) technology to deliver throughput and latency performance greater than what is possible with wide parallel bus technology.

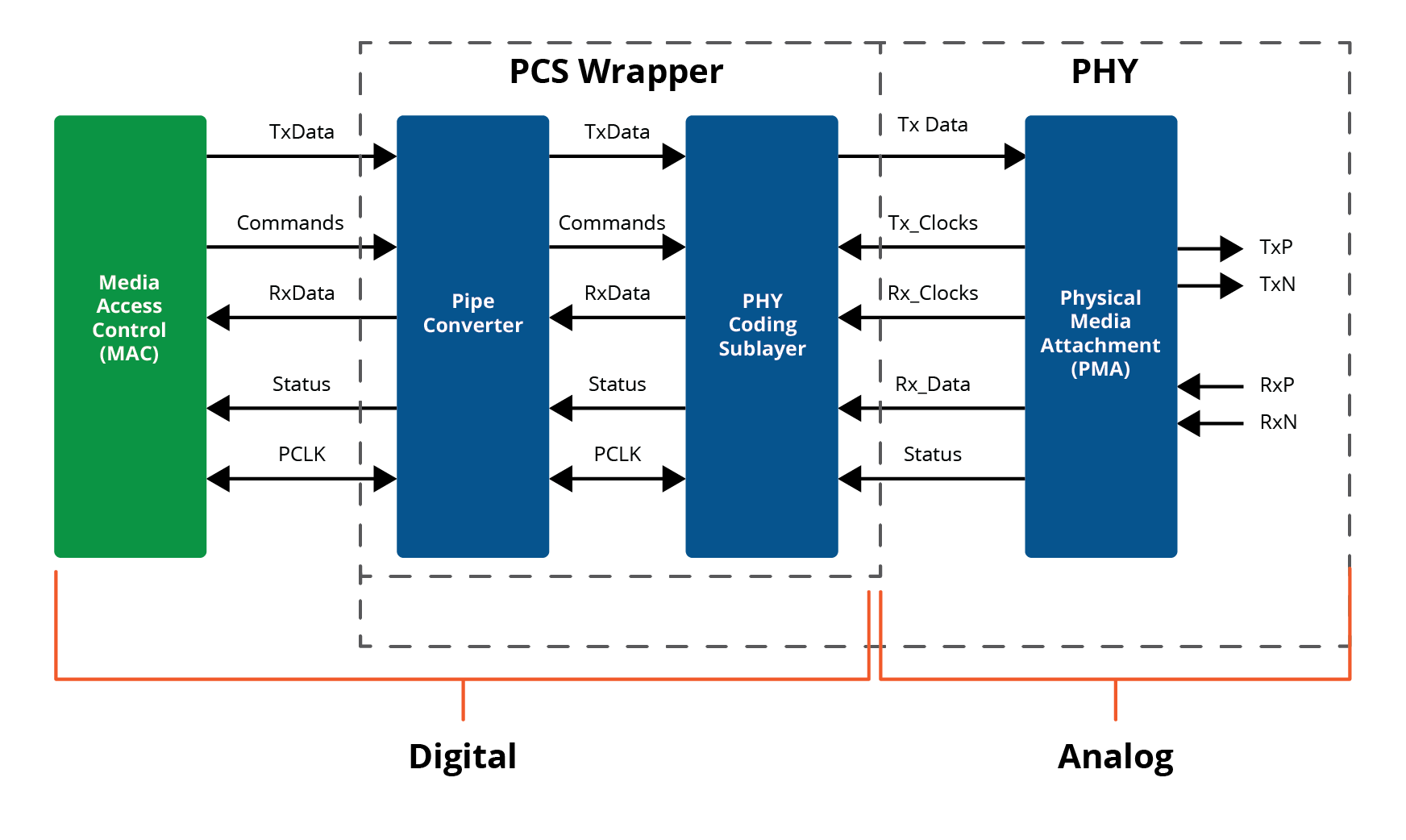

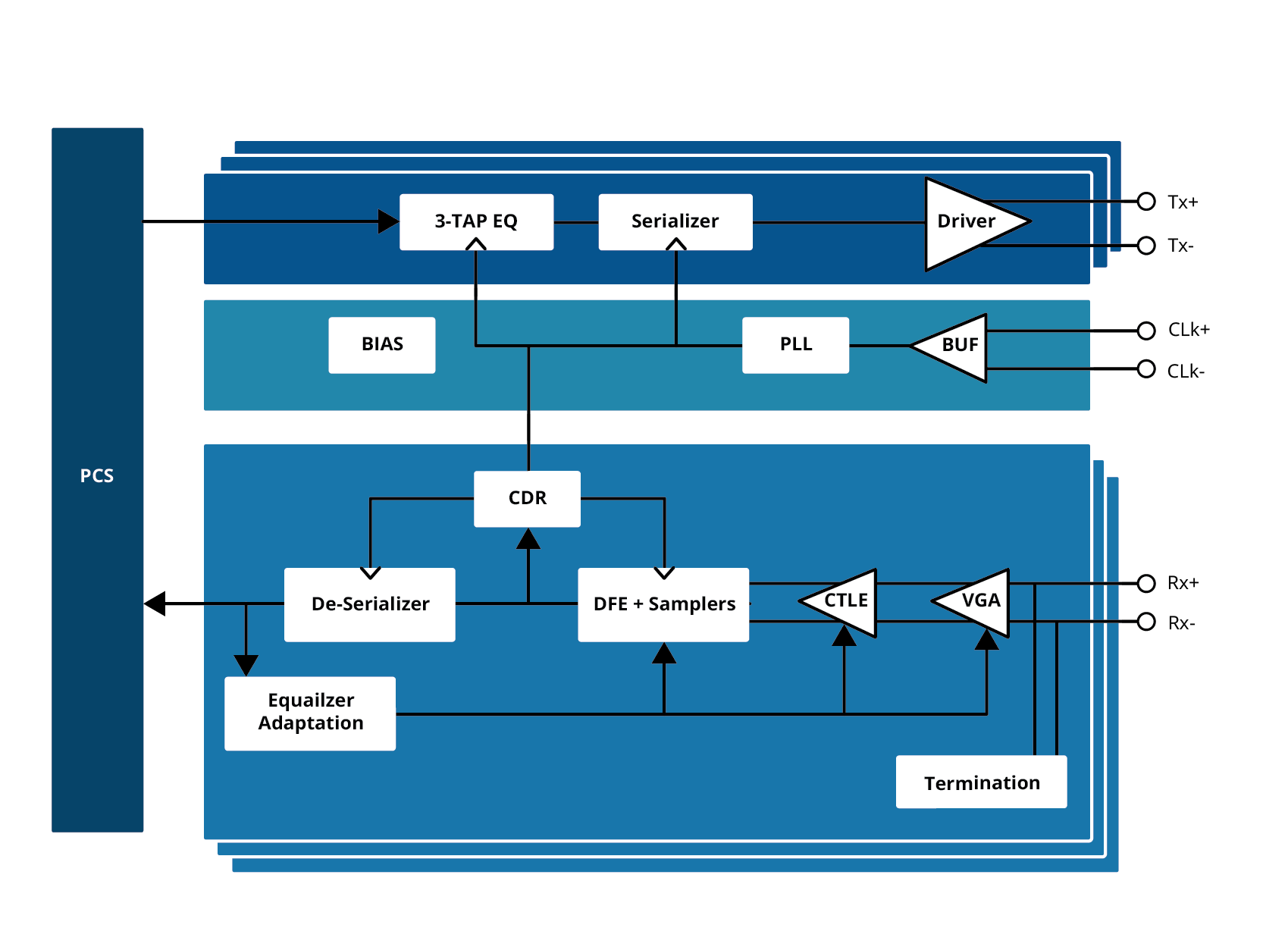

Terminus Circuits offers best-in-class PHY IP for PCIe 4.0/3.0/2.0. The PHY is designed for low latency, low power, small form factor, high interface speeds for high performance computing. The PHYs comes complete with a physical media attachment (PMA) hard macro that supports PCIe 4.0, 3.0, and 2.0 protocols and a physical coding sublayer (PCS) and soft macro for PCIe that is PIPE4.3 compliant.

Offerings:

-

- • Quad PCIe 16/8/5/2.5 Gbps per lane

- • Tight control over termination resistor (~50 Ohm) with on chip calibration

- • Tight skew control of 1UI between lanes of the PMA

- • 3-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

- • Lowest latency

- • Continuous time linear equalizer (CTLE) with programmable settings providing up to 12dB gain peaking at Nyquist frequencies

- • Programmable/automatic calibration of key circuits (pre-emphasis, eye-diagram monitoring / DFE tap calibration / offset calibration)

- • CDR logic for better data alignment and locking

- • Support for bifurcation and quadfurcation modes

- • 3-tap Rx DFE (decision feedback equalizer)

- • Programmable internal/external loopback modes between TX and RX

- • SRnS (Separate Reference no Spread) support

- • Includes ESD structures

- • Operation across a wide temperature range (-40 C to +125 C)

USB 3.1 is the most recent version of the USB (Universal Serial Bus) standard for connecting electronic devices in host and device mode. USB 3.1 IP is targeted for integration into SoCs for media storage, and playback devices requiring faster bandwidth between PCs and portable electronic devices.

Terminus Circuits offers best-in-class SerDes IP for USB 3.1 PHY. The PHY is designed for low latency, low power, small form factor, high interface speeds for high performance computing. The PHYs comes complete with a physical media attachment (PMA) hard macro that supports USB 3.0 and USB3.1 protocols, a physical coding sublayer (PCS) and soft macro for USB that is PIPE4.2 compliant.

- • Parallel data widths of 8bits and 16bits

- • QUAD configuration (4TX and 4RX), Single lane configuration (1TX and 1RX)

- • Support signal loss and receiver detection using programmable multi-tap & de-emphasis

- • Support 1m cable

- • High speed low jitter (0.17UI) 10GHz PLL

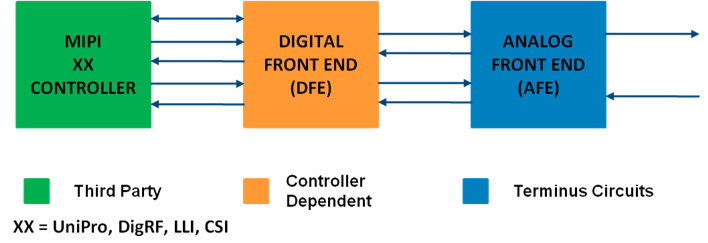

MIPI M-PHY HS Gear 4 IP is compliant with the MIPI serial communication protocol for use in mobile systems where performance, power, and efficiency are key criteria. It is the foundation for several upper layer protocols which manage complex data transfer functions. Each of these protocols is optimized for its particular purpose, such as data storage, data transfer, display, camera, memory sharing, and radio interface. Scalability and modularity are also important features of the MIPI M-PHY, as these features allow designers to more easily adapt to evolving system and application requirements.

- Supports MIPI CSI-3, MIPI DigRF, MIPI LLI, and MIPI UniPro

- Adopted by

- PCI SIG for M-PCIe

- USB IF for SSIC

- Supports Electrical Idle presentation with fast Electrical Idle Entry and Exit

Functional Block Diagram

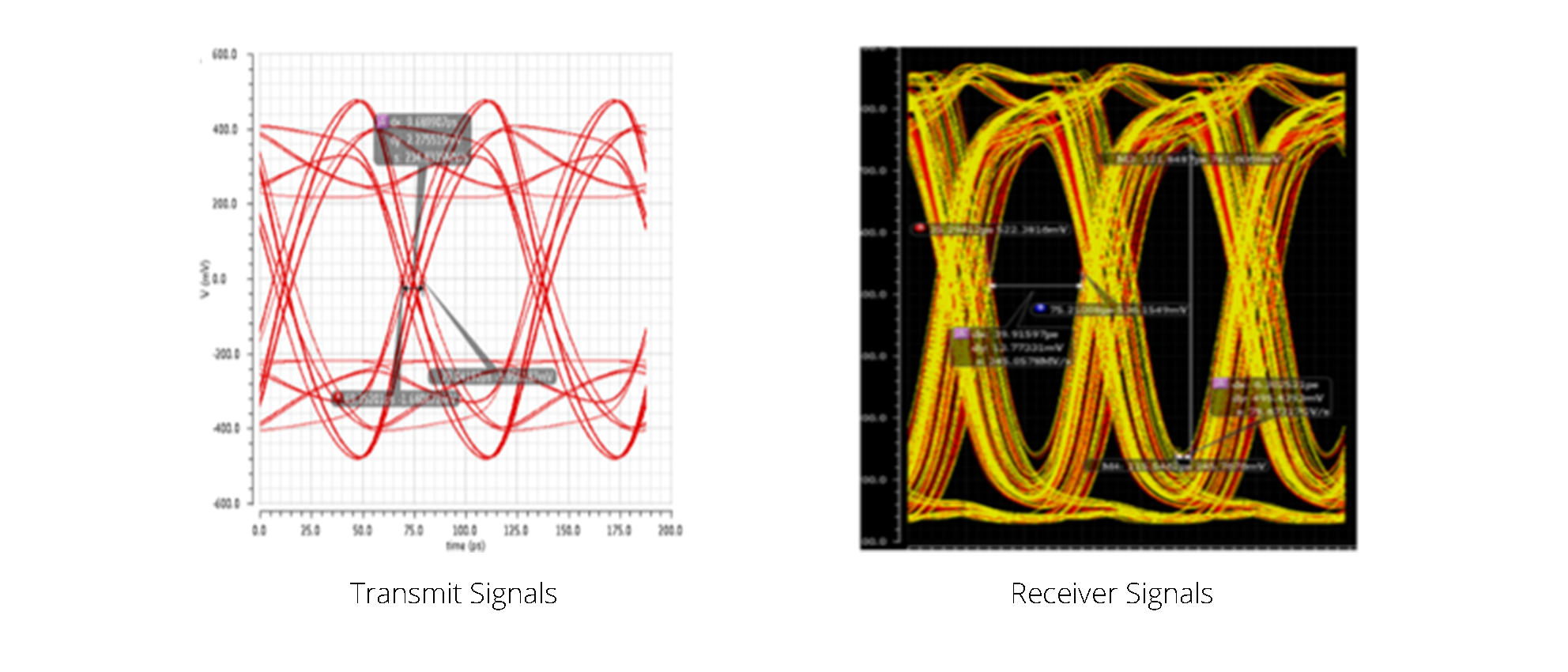

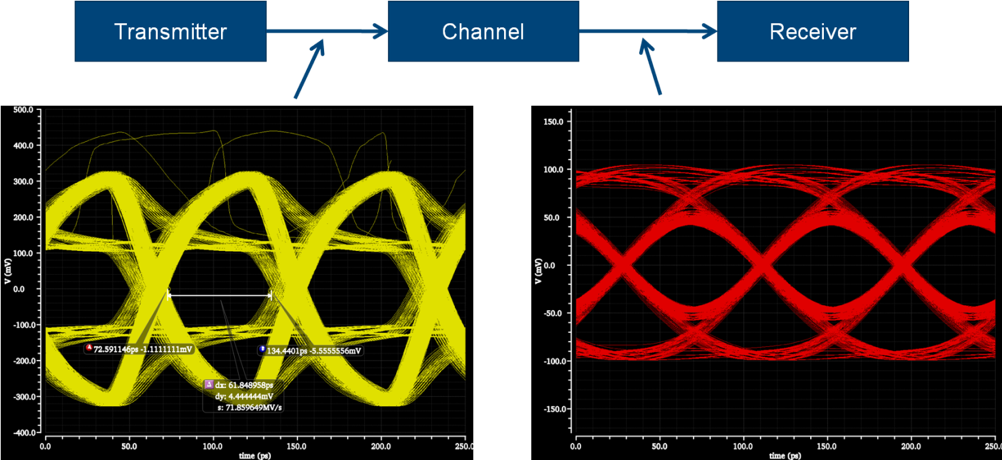

Functional Eye Diagram

The eye diagrams are given for the PRBS data pattern with the MIPI Reference-1 channel model.

Highlights

- Supports high speed data transfer G4A/B and backward compatible

- Multi-lane compatible

- Supports 4 reference clocks as per MIPI 4.1 specification

- PWM G1-G7 Signalling for Low Speed [LS] data

- Supports LS burst, HS burst, STALL, SLEEP, HIBERN8 states

- Supports squelch detection

- In-built reference-less oscillator to support PWM operation

- Supports all power down states

- 2 lane configuration to support 23.32Gbps or independent lanes

- Supports Receiver Detect

- Auto-Calibration of termination resistance

- Programmable internal/external loopback modes between Tx and Rx.

- Standby / power down mode

- Modular design

- Low silicon surface

- Operating temperature -40oC to 125oC

Deliverables

- GDS II Layouts

- LEF abstracts

- CDL netlists

- Liberty timings

- Verilog description

- Verilog based AFE Models

- A full datasheet

- An integration note

Terminus Circuits SerDes PHY IP meets the requirements of broad range of market segments including network communication, PC interconnect, data storage, enterprise routers, servers, industrial & test equipment, defence and aerospace etc. With seamless interoperability with available controllers it provides unique solution to customer’s system applications.

Terminus Circuits offers low power, low latency, integrated clocking and small footprint SerDes Quad PHY IP that supports one, two, four lanes per macro configuration.

| Standards | Data Rate (Gbps) | Organization |

| PCI Express Gen4/3/2/1 | 16/8/5/2.5 | PCI-SIG |

| USB 3.1 Gen2/1 | 10/5 | USB.org |

| SATA Gen 3/2/1 | 6/3/1.5 | SATA |

| 10GBase-KX4 | 3.125 | IEEE |

| 1000Base-KX | 1.25 | IEEE |

| 10GBase-KR / XFI | 10.3125 | IEEE |

| XAUI | 3.125 | IEEE |

| DisplayPort | 8.1 – 1.6 | VESA |

| HSSTP | 12.5 | ARM |

| EPON/GPON/XGPON | 1.25 / 2.488 / 9.95 | IEEE |

| SGMII/QSGMII | 1.25/5.0 | Cisco |

Offerings:

- • Configurable parallel data rate of 8 /10 / 16 / 20 / 32 / 40 / 64 / 80

- • Input reference 5MHz to support 2.5/5/10G data rates

- • Tight control over termination resistor (~50 Ohm) with on chip calibration

- • Tight skew control of 1UI between lanes of the PMA

- • Multi-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

- • Lowest latency

- • Continuous time linear equalizer (CTLE) with programmable settings providing up to 12dB gain peaking at Nyquist frequencies

- • Programmable/automatic calibration of key circuits (pre-emphasis, eye-diagram monitoring / DFE tap calibration / offset calibration)

- • CDR logic for better data alignment and locking

- • Support for bifurcation and quadfurcation modes

- • Multi-tap Rx DFE (decision feedback equalizer)

- • Programmable internal/external loopback modes between TX and RX

- • SRnS (Separate Reference no Spread) support

- • Includes ESD structures

- • Operation across a wide temperature range (-40 C to +125 C)

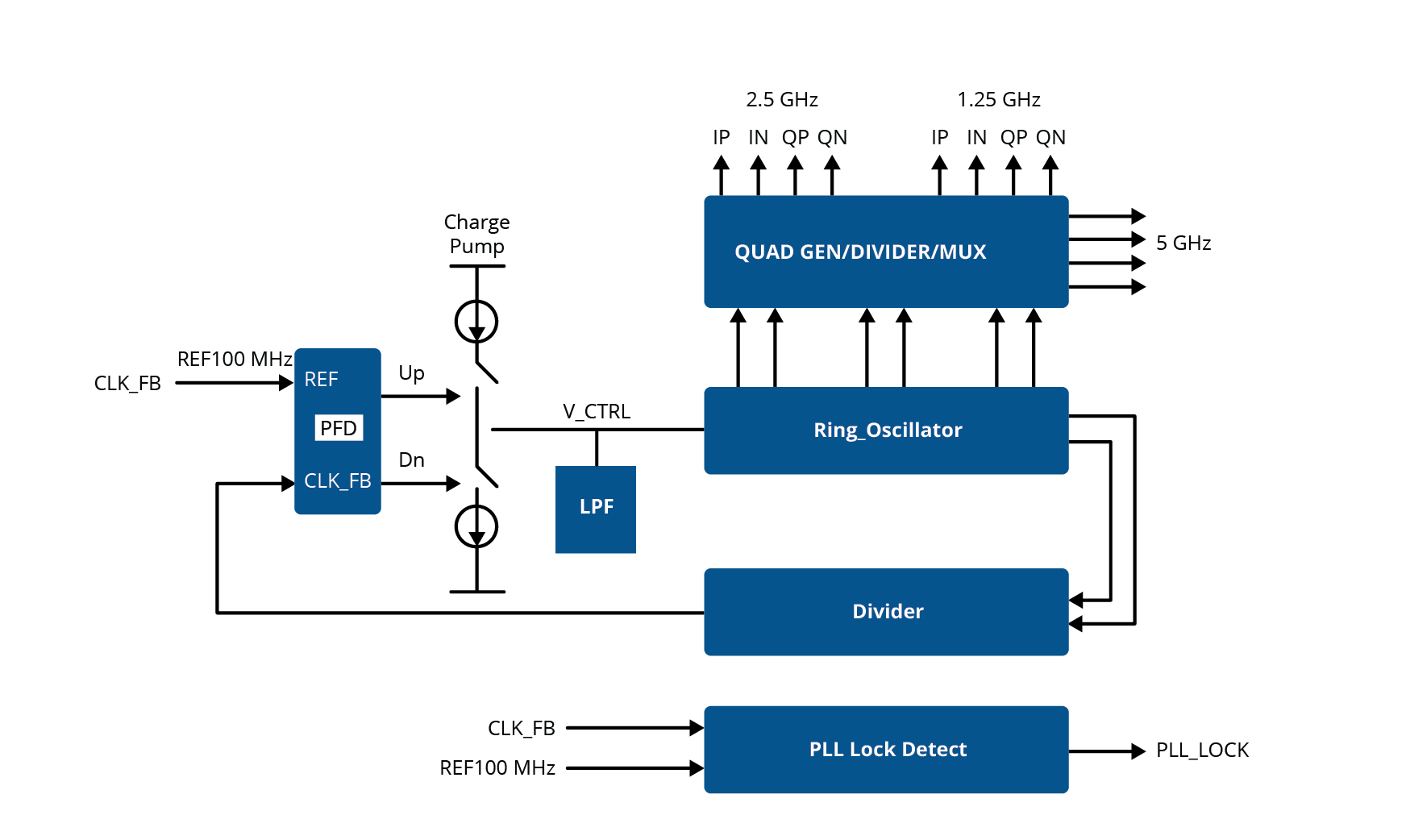

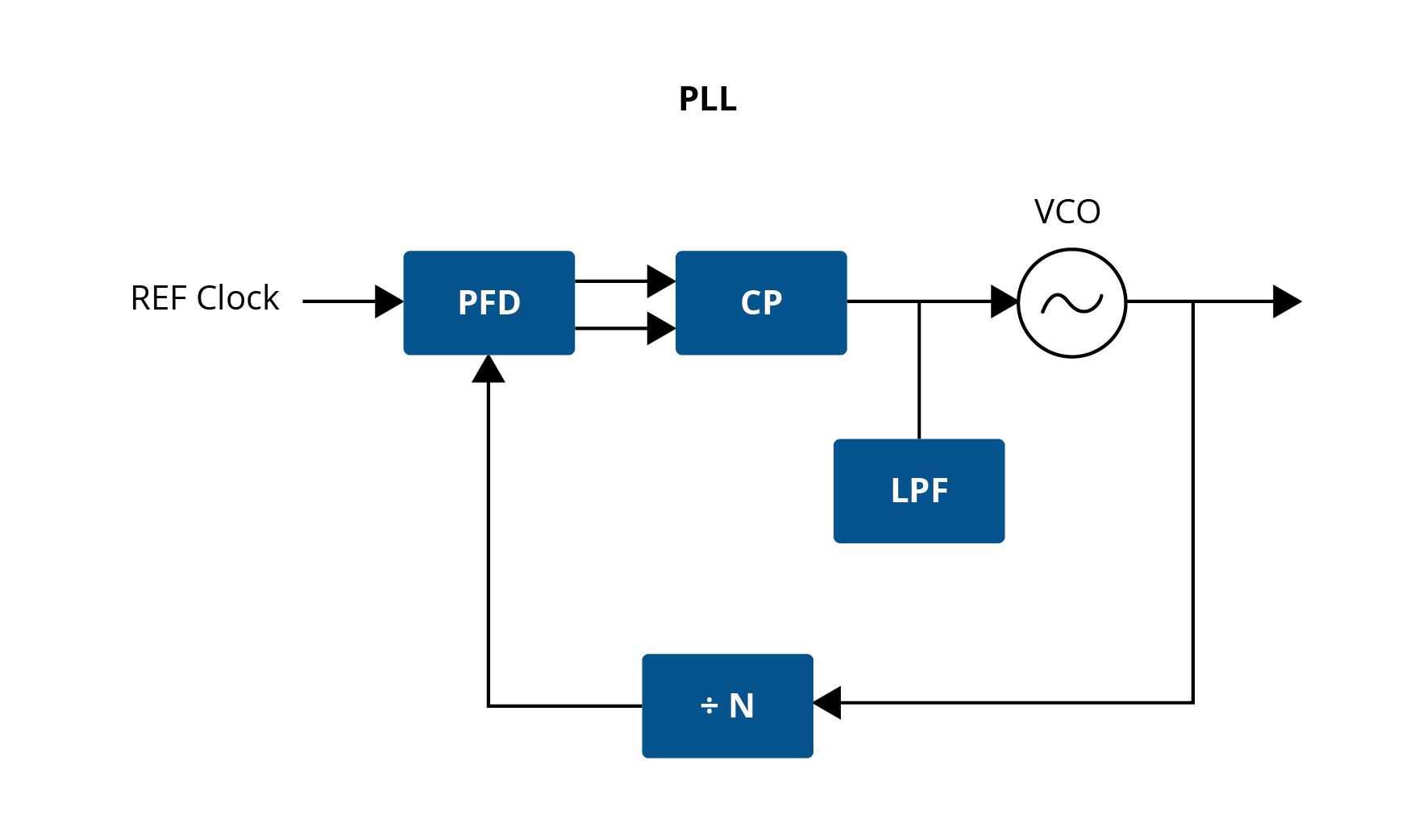

Low Jitter DIGITAL PLL – 1.25G/2.5G/5G

The Multiband Quadrature frequency synthesizer generates three frequencies 1.25G / 2.5G / 5G. The frequency outputs is applicable for USB 3.0 / 3.1 and WiFi Transceivers.

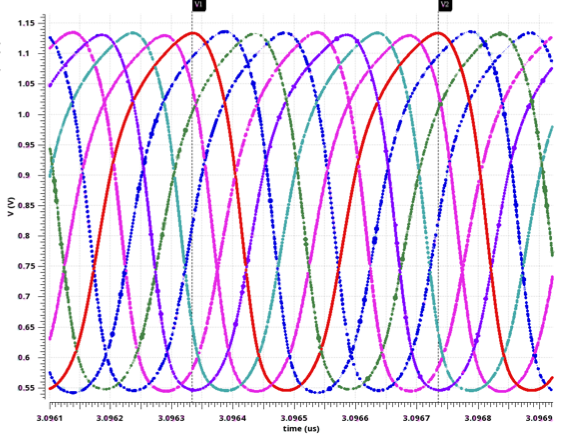

Clock output Waveform

Offering

-

• Type II, 3rd order low jitter PLL

-

• Auto calibration for process and temperature

-

• Programmable frequency using CSR registers

-

• 1.25GHz/2.5GHz/5GHz quadrature clocks

-

• Operating temperature -40 to 125

-

• Standby / power down mode

-

• Low silicon surface

Applications

-

• Clock multiplication

-

• Clock for High speed generators for SerDes PHY

-

• Clock Recovery

Deliverables

-

• GDS II Layouts

-

• LEF abstracts

-

• CDL netlists

-

• Liberty timings

-

• Verilog description

-

• Datasheet

-

• Integration note

The High Speed 16GHz PLL generates a low jitter frequency outputs. We have 2 PLL offering with 16 GHz and 10GHz respectively. These clocks could be used to produce quadrature outputs and the frequency outputs are applicable for PCI Express Gen3.0/ Gen4.0 PHY transceivers and SerDes.

Clock output Waveform

Offering

-

• Type II ,3rd order low jitter PLL

-

• Auto calibration for process and temperature (USP)

-

• Programmable frequency using CSR registers

-

• 8/10/16GHz quadrature clocks

-

• Operating temperature -40 to 125

-

• Standby / power down mode

-

• Low silicon surface

Applications

-

• Clock multiplication

-

• Clock for High speed generators for SerDes PHY

-

• Clock Recovery

Deliverables

-

• GDS II Layouts

-

• LEF abstracts

-

• CDL netlists

-

• Liberty timings

-

• Verilog description

-

• Datasheet

-

• Integration note